# 組込みシステムのための浮動小数点演算の実装と評価

指導教員:市川周一 学籍番号: 043732 畑 尚志

### 1 背景と目的

Programmable Logic Controller (PLC) は ,シーケンス制御に用いられる制御用計算機である . PLC プログラムによる制御は広く行われているが ,近年 ,大規模システムにおける速度不足が問題になっている . そこで , PLC プログラムを論理回路に変換し ,再構成可能なハードウェアである Field Programmmable Gate Array (FPGA) で実現することが検討されている .

池田 [1] は、PLC 命令列をハードウェア記述言語 VHDL に変換して FPGA 上に実装する方法を示した.池田の手法では、PLC プログラム内の演算命令は、対応するハードウェア演算器に変換される.PLC 命令の多くはビット演算命令であるため、このような実装でも論理規模はさほど大きくならない[1].

しかし PLC プログラムでは,フィードバック制御等で浮動小数点演算命令を使用することがある.これらをハードウェアに変換すると,浮動小数点演算ユニット (FPU) が必要になる.FPU の論理規模は大きく,遅延時間も大きいため,FPGA による実装が可能であるか明らかでない.本研究の目的は,浮動小数点演算を行う制御プログラムを FPGA 上に実装した場合の論理規模と処理時間を,定量的に検討することである.浮動小数点演算を利用する制御プログラムの例としては PID 制御のフィードバックループを用いる.

### 2 PID 制御プログラム

PID 制御はフィードバック制御の一種で,入力値の制御を,出力値と目的値の偏差,その積分,および微分によって行う方法である.目標値をP,サンプリング時刻を $t_n$ ,現在値を $F(t_n)$ とあらわすとき,時刻 $t_n$ における操作量 $M_n$  は以下の式で計算される.ここで $E_n$  は偏差, $K_1,K_2,K_3$  はフィードバックゲイン (定数)である.以下の式では演算回数を節約するため,典型的な計算式を変形して定数項をまとめてある. $E_{n-1},M_{n-1}$ は,それぞれ時刻 $t_{n-1}$ における偏差と操作量である.PID 制御では, $F(t_n)$ が充分にPに近づくまで下記の処理を繰り返す.

$$E_n = P - F(t_n) \tag{1}$$

$$\Delta M_n = K_1 E_n + K_2 E_{n-1} + K_3 E_{n-2} \tag{2}$$

$$M_n = M_{n-1} + \Delta M_n \tag{3}$$

#### 3 回路設計

本研究では、評価プラットホームとして Xilinx 社の Virtex-II FPGA [3] を使用し、組込みプロセッサとして Xilinx のソフトプロセッサ MicroBlaze を採用した . MicroBlaze は、FPGA の内蔵メモリ BlockRAM にアクセスするための Local Memory Bus (LMB)、デバイスに高速アクセス可能な Fast Simplex Link (FSL)、メモリマップ I/O を接続する On-chip Peripheral Bus (OPB)、の3種類の入出力バスを持つ、今回の実装では、OPBにデバッグモジュール、タイマ、シリアル通信コントローラ、外部 RAM コントローラ、BlockRAM コントローラを接続し、LMB にキャッシュ(命令 8KB、データ 8KB) を接続した、外付け FPU には Marcus の FPU [2] を採用する.

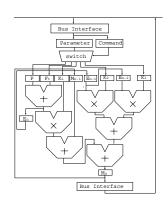

図 1: 回路:PID

本研究では、PID 制御 1 回分の処理時間を、以下の 8 つの実装方法について測定する。(1) FPU なしの MicroBlaze でソフトウェアにより実現 (MBs)、(2) FPU つき MicroBlaze のソフトウェアで実現 (MBh)、(3) Marcus の加算器と乗算器を FSLに接続 (F\_M+A)、(4) 積和演算器を FSLに接続 (F\_MAU)、(5) PID 専用演算器 (図 1)を FSLに接続 (F\_PID)、(6) 加算器と乗算器を OPBに接続 (O\_M+A)、(7) 積和演算器を OPBに接続 (O\_MAU)、(8) PID 専用演算器 (図 1)を OPBに接続 (O\_PID)。

#### 4 評価

評価結果を表 1 にまとめる . 回路生成を Xilinx ISE 7.1.03i で行い , 回路規模と動作周波数を評価した . 得られた回路は MULTI3000 ボード (XC2V3000 搭載, クロック 50MHz) にダウンロードし , 実機で処理時間を測定した . MBs と MBh の処理時間はデータに依存するため , 擬似乱数を入力してプログラムを 100 回実行し , 平均処理時間を求めた . FSL や OPB に演算器を付加した場合は , OPB 上のタイマで所要サイクル数を測定した .

評価の結果,外部バスに FPU を接続した回路は MBh に比べ Slice 数が  $8\%(F\_MAU) \sim 107\%(O\_PID)$  増加し,処理速度は 47 倍  $(O\_M+A) \sim 234$  倍  $(F\_PID)$  に向上した.PID 制御に関して言えば,外部バスへの FPU 接続には大きな効果が見込まれる.特に専用回路の接続による性能向上は大きいので,命令列から専用回路を生成する手法は有望であると期待される.

組込みシステムでは,PID 制御が固定小数点演算で行われる場合もある. $F_PID$  の FPU を整数演算器に置き換えて同様の評価をした結果,MBs に対し Slice 数が 32%増加し,処理速度は約 77 倍になった.

# 参考文献

- [1] 池田亮: "PLC プログラムのハードウェア変換ツールに関する研究," 豊橋技術科学大学 知識情報工学系 修士論文 (2005).

- [2] G. Marcus: "Floating Point Adder and Multiplier," http://www.opencores.org/cvsweb.shtml/fpuvhdl/(2005).

- [3] Xilinx, Inc.: "Virtex<sup>TM</sup>-II Platform FPGAs: Complete Data Sheet," DS031, http://www.xilinx.com/ (2003).

表 1: 測定結果

|               | MBs      | MBh      | F_M+A | F_MAU | F_PID | O_M+A | O_MAU | O_PID | XC2V3000 |

|---------------|----------|----------|-------|-------|-------|-------|-------|-------|----------|

| 命令数           | 69       | 59       | 35    | 26    | 5     | 46    | 32    | 6     | _        |

| クロックサイクル数     | 21684.63 | 18653.56 | 192   | 156   | 66    | 336   | 247   | 80    | _        |

| 動作可能周波数 (MHz) | 60.55    | 60.91    | 50.00 | 52.78 | 50.49 | 51.05 | 51.46 | 50.06 | _        |

| 処理時間 (μs)     | 358.12   | 306.27   | 3.84  | 2.96  | 1.31  | 6.58  | 4.80  | 1.60  | _        |

| 18x18MUL      | 3        | 7        | 7     | 7     | 15    | 7     | 7     | 15    | 96       |

| BlockRAM      | 14       | 14       | 14    | 14    | 14    | 14    | 14    | 14    | 96       |

| Slice         | 1459     | 2108     | 2424  | 2277  | 4254  | 2758  | 2427  | 4371  | 14336    |